In addition to the global clock buffer, Spartan-6 also includes a clock buffer that drives the high-speed I/O clock area.

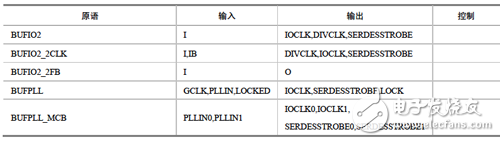

The primitives of the I/O clock buffer are shown in Table 2-9.

Table 2-9 I/O Clock Buffer Primitives

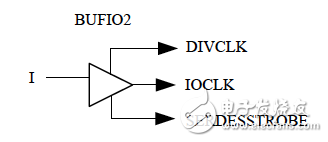

(1) BUFIO2.

BUFIO2 receives the GCLK clock input and generates two clock outputs and a strobe that drives IOSERDES2, as shown in Figure 2-9.

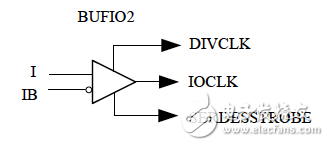

(2) BUFIO2_2CLK.

The functions of BUFIO2_2CLK and BUFIO2 are almost the same, except that the input of BUFIO2_2CLK is two single-ended clocks or a pair of differential clocks (output of IBUFDS_DIFF_OUT), as shown in Figure 2-10.

Figure 2-9 Primitives of BUFIO2

Figure 2-10 Primitives of BUFIO2_2CLK

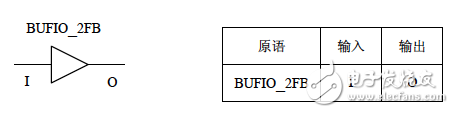

(3) BUFIO_2FB.

The BUFIO2FB is a single-input, single-output buffer with an output attribute that controls the output delay, as shown in Figure 2-11. When the attribute DIVIDE_BYPASS is set to TRUE, BUFIO_2FB is equivalent to the BUFIO2 bypass delay;

When the attribute DIVIDE_BYPASS is set to FALSE, the delay of BUFIO_2FB is similar to the DIVCLK output of BUFIO2, keeping the output of BUFIO2 and the phase of BUFIO_2FB aligned.

Figure 2-11 Primitives of BUFIO_2FB

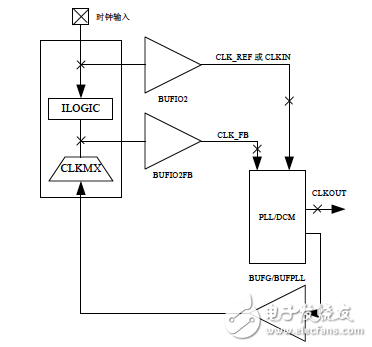

The BUFIO_2FB buffer provides a good solution for the clock routing delay of the CMT (PLL or DCM) reference input CLKIN and the feedback input CLKFB. When using the CMT feedback path, ISE will automatically insert the BUFIO_2FB and BUFIO2 buffers, as shown in Figure 2-12.

Figure 2-12 BUFIO_2FB Buffer and Clock Routing Delay Match

(4) BUFPLL.

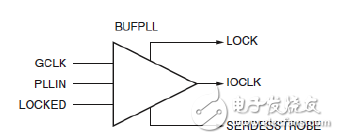

Figure 2-13 shows the primitives of BUFPLL, which are used to drive high-speed I/O and clock the ISERDES2 and OSERDES2.

It aligns the PLL's LOCK output with the GCLK, SERDES strobe, and PLL clock. The IOCLK is just the version that passes the input clock through the first level buffer. The LOCK output signal actually has the same function as the PLL's LOCKED signal. The difference is that the LOCK does not go high until the PLL locks and the BUFPLL aligns the SERDES strobe signal.

Figure 2-13 Primitives of BUFPLL

The Spartan-6 device has two BUFPLLs per BANK, dedicated to the PLL, and is not recommended for use as a logic clock.

(5) BUFPLL_MCB.

BUFPLL_MCB is dedicated to the integrated memory controller in Spartan-6. For a detailed description, please refer to the Spartan-6 Memory Controller User Manual on the supplied CD-ROM.

China Smart Monitoring Box,Intelligent Monitoring Box,Security System Smart Box,Intelligent Monitoring Smart Box, we offered that you can trust. Welcome to do business with us.

The intelligent monitoring box is a domestic monitoring and management product developed for many years to meet the management information needs of smart cities, public safety, traffic track monitoring, power, oil pipeline monitoring and other fields. In addition to meeting the basic functional requirements of the original Communication Protection Box, this product ensures the intelligent monitoring box and related systems through the Internet of Things technology, smart city information management technology, modular layout, lightning protection system design, and complete and powerful data applications. The reliability, continuity and intelligence requirements of operating equipment improve the online rate of related equipment; this equipment is an all-weather outdoor electrical equipment protection box used in the open environment, with rainproof, dustproof, ventilation and heat dissipation, anti-aging, anti-lightning, Anti-electromagnetic interference and other functions.

Smart Monitoring Box,Intelligent Monitoring Box,Security System Smart Box,Intelligent Monitoring Smart Box

Shenzhen Scodeno Technology Co.,Ltd , https://www.scodenonet.com